### <u>Voltage Regulator</u> - Low Dropout

### 300 mA

### MC33275, NCV33275

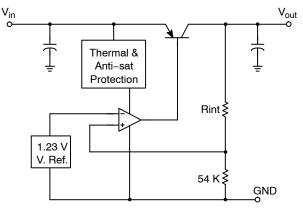

The MC33275 series are micropower low dropout voltage regulators available in a wide variety of output voltages as well as packages, SOT-223, SOP-8, DPAK, and DFN 4x4 surface mount packages. These devices feature a very low quiescent current and are capable of supplying output currents up to 300 mA. Internal current and thermal limiting protection are provided by the presence of a short circuit at the output and an internal thermal shutdown circuit.

Due to the low input-to-output voltage differential and bias current specifications, these devices are ideally suited for battery powered computer, consumer, and industrial equipment where an extension of useful battery life is desirable.

#### Features

- Low Input-to-Output Voltage Differential of 25 mV at  $I_0 = 10$  mA, and 260 mV at  $I_0 = 300$  mA

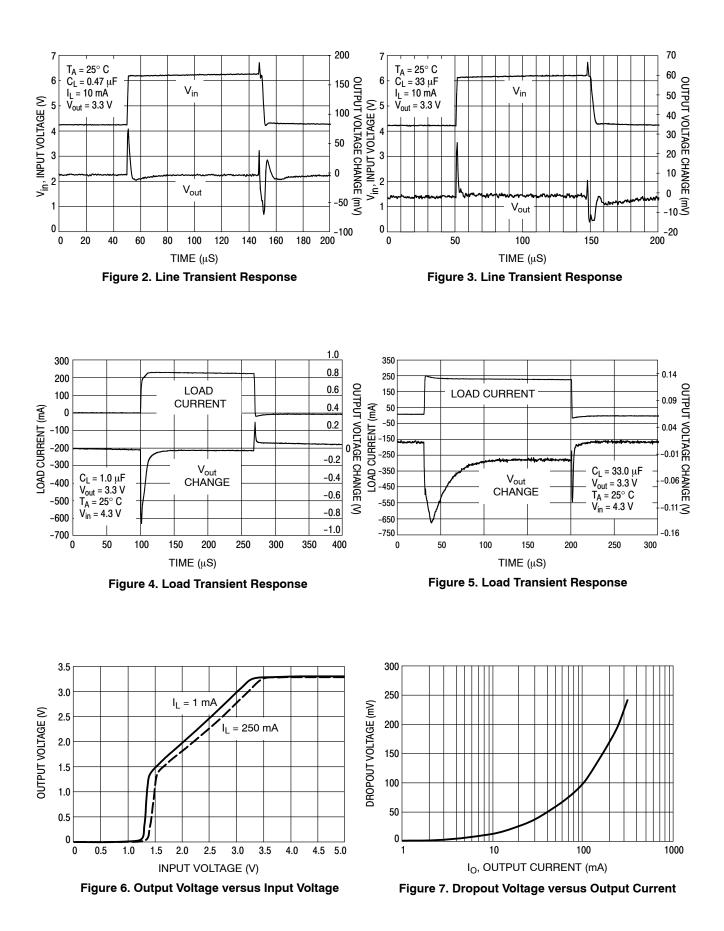

- Extremely Tight Line and Load Regulation

- Stable with Output Capacitance of only 0.33  $\mu F$  for 2.5 V Output Voltage

- Internal Current and Thermal Limiting

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb–Free Devices

#### Applications

- Battery Powered Consumer Products

- Hand-Held Instruments

- Camcorders and Cameras

This device contains 41 active transistors

#### Figure 1. Simplified Block Diagram

#### LOW DROPOUT MICROPOWER VOLTAGE REGULATOR

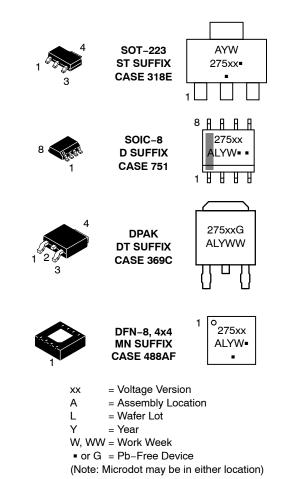

#### MARKING DIAGRAMS

ORDERING INFORMATION

See detailed ordering and shipping information on page 10 of this data sheet.

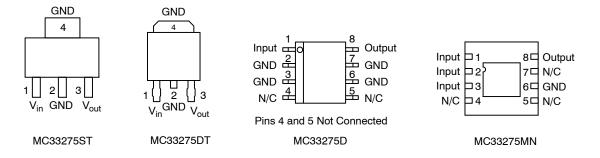

#### **PIN CONNECTIONS**

#### MAXIMUM RATINGS

| Rating                                                                                                                         | Symbol                      | Value              | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|------|

| Input Voltage                                                                                                                  | V <sub>CC</sub>             | 13                 | Vdc  |

| Power Dissipation and Thermal Characteristics                                                                                  |                             |                    |      |

| $T_A = 25^{\circ}C$                                                                                                            |                             |                    |      |

| Maximum Power Dissipation                                                                                                      | PD                          | Internally Limited | W    |

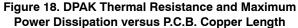

| Case 751 (SOIC-8) D Suffix<br>Thermal Resistance, Junction-to-Ambient                                                          | $R_{	extsf{	heta}JA}$       | 160                | °C/W |

| Thermal Resistance, Junction-to-Case                                                                                           | $R_{\theta JC}$             | 25                 | °C/W |

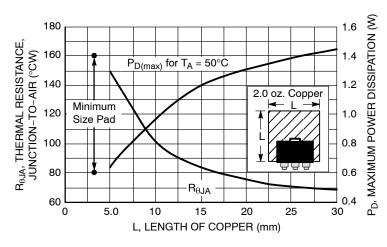

| Case 318E (SOT-223) ST Suffix                                                                                                  | 1,410                       | 20                 | 0,11 |

| Thermal Resistance, Junction-to-Air                                                                                            | $R_{\theta JA}$             | 245                | °C/W |

| Thermal Resistance, Junction-to-Case                                                                                           | R <sub>0JC</sub>            | 15                 | °C/W |

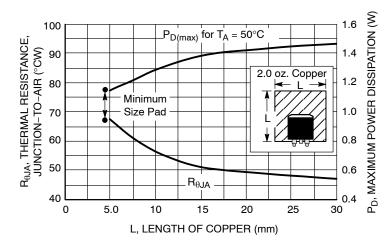

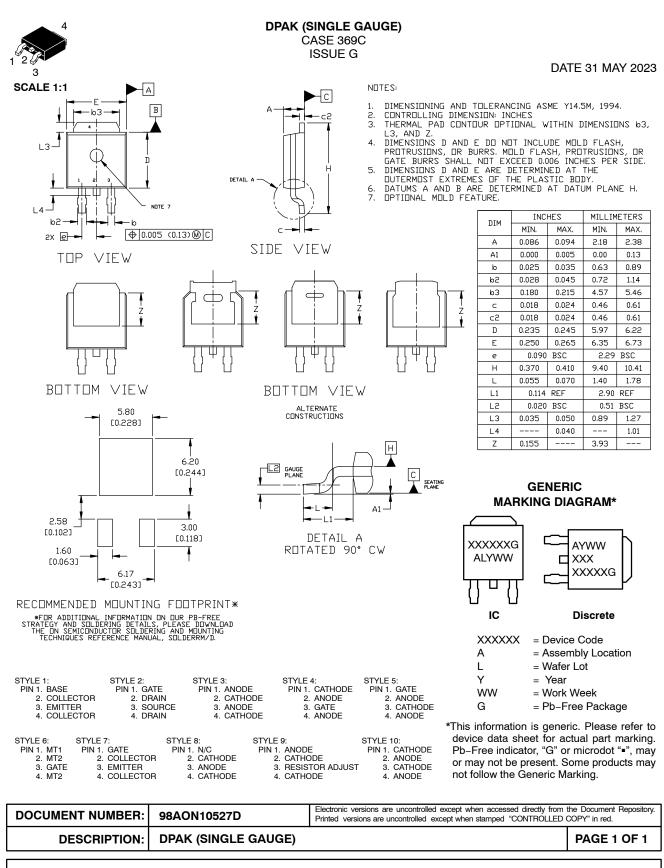

| Case 369A (DPAK-3) DT Suffix                                                                                                   |                             |                    |      |

| Thermal Resistance, Junction-to-Air                                                                                            | $R_{	extsf{	heta}JA}$       | 92                 | °C/W |

| Thermal Resistance, Junction-to-Case                                                                                           | $R_{	ext{	heta}JC}$         | 6.0                | °C/W |

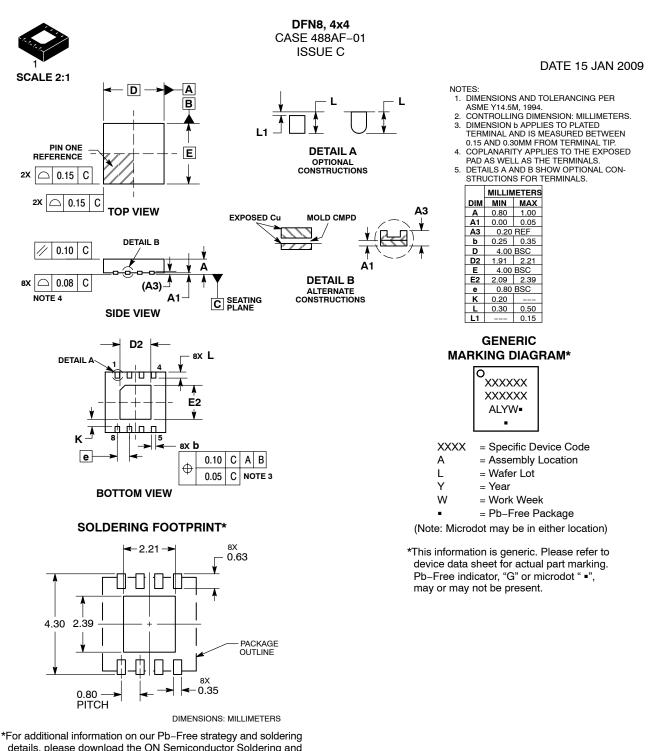

| Case 488AF (DFN-8, 4x4) MN Suffix                                                                                              | Б                           | 183                | °C/W |

| Thermal Resistance, Junction-to-Air (with 1.0 oz PCB cu area)<br>Thermal Resistance, Junction-to-Air (with 1.8 oz PCB cu area) | R <sub>0JA</sub>            | 93                 | °C/W |

| Thermal Resistance, Junction-to-Case                                                                                           | R <sub>θJA</sub><br>psi–JC* | 9.0                | °C/W |

|                                                                                                                                | p3i=00                      |                    | 0,11 |

| Output Current                                                                                                                 | Ι <sub>Ο</sub>              | 300                | mA   |

| Maximum Junction Temperature                                                                                                   | TJ                          | 150                | °C   |

| Operating Ambient Temperature Range                                                                                            | T <sub>A</sub>              | – 40 to +125       | °C   |

| Storage Temperature Range                                                                                                      | T <sub>stg</sub>            | – 65 to +150       | °C   |

| Electrostatic Discharge Sensitivity (ESD)                                                                                      | ESD                         |                    | V    |

| Human Body Model (HBM)                                                                                                         |                             | 4000               | . ·  |

| Machine Model (MM)                                                                                                             |                             | 400                |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

\*"C" ("case") is defined as the solder-attach interface between the center of the exposed pad on the bottom of the package, and the board to which it is attached.

|                                | Characteristic                                                                                            | Symbol                           | Min   | Тур  | Max   | Unit  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|-------|------|-------|-------|

| Output Voltage<br>2.5 V Suffix | $I_{O} = 0 \text{ mA to } 250 \text{ mA}$<br>$T_{A} = 25^{\circ}\text{C}, V_{in} = [V_{O} + 1] \text{ V}$ | Vo                               | 2.475 | 2.50 | 2.525 | Vdc   |

| 3.0 V Suffix                   |                                                                                                           |                                  | 2.970 | 3.00 | 3.030 |       |

| 3.3 V Suffix                   |                                                                                                           |                                  | 3.267 | 3.30 | 3.333 |       |

| 5.0 V Suffix                   |                                                                                                           |                                  | 4.950 | 5.00 | 5.05  |       |

| 2.5 V Suffix                   | V <sub>in</sub> = [V <sub>O</sub> + 1] V, 0 < I <sub>O</sub> < 100 mA                                     |                                  | 2.450 | -    | 2.550 |       |

| 3.0 V Suffix                   | 2% Tolerance from $T_J = -40$ to $+125^{\circ}C$                                                          |                                  | 2.940 | -    | 3.060 |       |

| 3.3 V Suffix                   |                                                                                                           |                                  | 3.234 | -    | 3.366 |       |

| 5.0 V Suffix                   |                                                                                                           |                                  | 4.900 | -    | 5.100 |       |

| Line Regulation                | $V_{in} = [V_O + 1] V \text{ to } 12 V, I_O = 250 \text{ mA},$<br>All Suffixes $T_A = 25^{\circ}\text{C}$ | Reg <sub>line</sub>              | -     | 2.0  | 10    | mV    |

| Load Regulation                | $V_{in} = [V_O + 1] V$ , $I_O = 0 mA$ to 250 mA,<br>All Suffixes $T_A = 25^{\circ}C$                      | Reg <sub>load</sub>              | -     | 5.0  | 25    | mV    |

| Dropout Voltage                |                                                                                                           | V <sub>in</sub> – V <sub>O</sub> |       |      |       | mV    |

| l <sub>O</sub> = 10 mA         | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } +125^{\circ}{\rm C}$                                          |                                  | -     | 25   | 100   |       |

| l <sub>O</sub> = 100 mA        |                                                                                                           |                                  | -     | 115  | 200   |       |

| I <sub>O</sub> = 250 mA        |                                                                                                           |                                  | -     | 220  | 400   |       |

| l <sub>O</sub> = 300 mA        |                                                                                                           |                                  | -     | 260  | 500   |       |

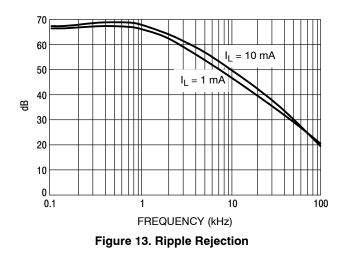

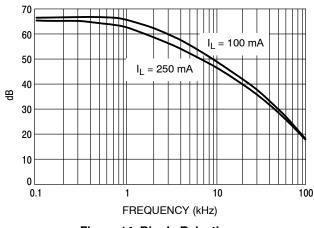

| Ripple Rejection (             | (120 Hz) V <sub>in(peak-peak)</sub> = [V <sub>O</sub> + 1.5] V to [V <sub>O</sub> + 5.5] V                | -                                | 65    | 75   | -     | dB    |

| Output Noise Volt              | age                                                                                                       | Vn                               |       |      |       | μVrms |

| C <sub>L</sub> = 1.0 μF        | I <sub>O</sub> = 50 mA (10 Hz to 100 kHz)                                                                 |                                  | -     | 160  | -     |       |

| C <sub>L</sub> = 200 μF        |                                                                                                           |                                  | -     | 46   | -     |       |

| <b>ELECTRICAL CHARACTERISTICS</b> | $(C_L = 1.0 \mu F, T_A = 25^{\circ}C)$ , for min/max values $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , No | te 1) |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|-------|

|-----------------------------------|----------------------------------------------------------------------------------------------------------|-------|

#### **CURRENT PARAMETERS**

| Quiescent Current ON Mode                                                     | $V_{in} = [V_O + 1] V, I_O = 0 mA$                | I <sub>QOn</sub>   | -           | 125                  | 200                  | μA |

|-------------------------------------------------------------------------------|---------------------------------------------------|--------------------|-------------|----------------------|----------------------|----|

| Quiescent Current ON Mode SAT<br>3.0 V Suffix<br>3.3 V Suffix<br>5.0 V Suffix | $V_{in} = [V_0 - 0.5] V, I_0 = 0 mA (Notes 2, 3)$ | I <sub>QSAT</sub>  | -<br>-<br>- | 1500<br>1500<br>1500 | 2000<br>2000<br>2000 | μΑ |

| Current Limit                                                                 | $V_{in} = [V_O + 1] V, V_O Shorted$               | I <sub>LIMIT</sub> | -           | 450                  | _                    | mA |

#### THERMAL SHUTDOWN

#### Thermal Shutdown

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

\_

\_

150

°C

\_

1. Low duty pulse techniques are used during test to maintain junction temperature as close to ambient as possible. 2. Quiescent Current is measured where the PNP pass transistor is in saturation.  $V_{in} = [V_0 - 0.5]$  V guarantees this condition.

3. For 2.5 V version,  $I_{QSAT}$  is constrained by the minimum input voltage of 2.5 V.

#### DEFINITIONS

**Load Regulation** – The change in output voltage for a change in load current at constant chip temperature.

**Dropout Voltage** – The input/output differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 100 mV below its nominal value (which is measured at 1.0 V differential), dropout voltage is affected by junction temperature, load current and minimum input supply requirements.

**Output Noise Voltage** – The RMS AC voltage at the output with a constant load and no input ripple, measured over a specified frequency range.

**Maximum Power Dissipation** – The maximum total dissipation for which the regulator will operate within specifications.

**Quiescent Current** – Current which is used to operate the regulator chip and is not delivered to the load.

**Line Regulation** – The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that the average chip temperature is not significantly affected.

**Maximum Package Power Dissipation** – The maximum package power dissipation is the power dissipation level at which the junction temperature reaches its maximum value i.e.  $150^{\circ}$ C. The junction temperature is rising while the difference between the input power (V<sub>CC</sub> X I<sub>CC</sub>) and the output power (V<sub>out</sub> X I<sub>out</sub>) is increasing.

Depending on ambient temperature, it is possible to calculate the maximum power dissipation and so the maximum current as following:

$$\mathsf{Pd} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}}}{\mathsf{R}_{\mathsf{\theta}\mathsf{J}\mathsf{A}}}$$

The maximum operating junction temperature  $T_J$  is specified at 150°C, if  $T_A = 25$ °C, then  $P_D$  can be found. By neglecting the quiescent current, the maximum power dissipation can be expressed as:

$$V_{out} = \frac{P_D}{V_{CC} - V_{out}}$$

The thermal resistance of the whole circuit can be evaluated by deliberately activating the thermal shutdown of the circuit (by increasing the output current or raising the input voltage for example).

Then you can calculate the power dissipation by subtracting the output power from the input power. All variables are then well known: power dissipation, thermal shutdown temperature and ambient temperature.

$$\mathsf{R}_{\theta \mathsf{J}\mathsf{A}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{D}}}$$

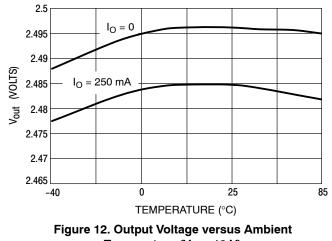

Ambient Temperature

Temperature (V<sub>in</sub> = V<sub>out</sub> + 1V)

Temperature (V<sub>in</sub> = 12 V)

Figure 14. Ripple Rejection

#### **APPLICATIONS INFORMATION**

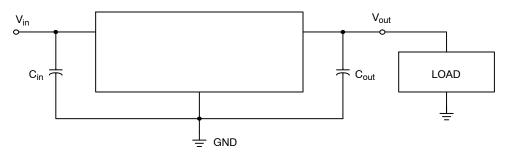

Figure 15. Typical Application Circuit

The MC33275 regulators are designed with internal current limiting and thermal shutdown making them user-friendly. Figure 15 is a typical application circuit. The output capability of the regulator is in excess of 300 mA, with a typical dropout voltage of less than 260 mV. Internal protective features include current and thermal limiting.

#### **EXTERNAL CAPACITORS**

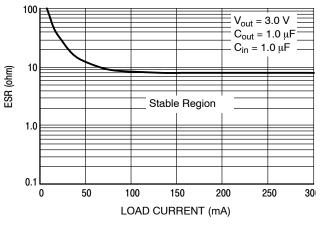

These regulators require only a 0.33  $\mu$ F (or greater) capacitance between the output and ground for stability for 1.8 V, 2.5 V, 3.0 V, and 3.3 V output voltage options. Output voltage options of 5.0 V require only 0.22 µF for stability. The output capacitor must be mounted as close as possible to the MC33275. If the output capacitor must be mounted further than two centimeters away, then a larger value of output capacitor may be required for stability. A value of 0.68 µF or larger is recommended. Most type of aluminum, tantalum, or multilayer ceramic will perform adequately. Solid tantalums or appropriate multilayer ceramic capacitors are recommended for operation below 25°C. An input bypass capacitor is recommended to improve transient response or if the regulator is connected to the supply input filter with long wire lengths, more than 4 inches. This will reduce the circuit's sensitivity to the input line impedance at high frequencies. A 0.33 µF or larger tantalum, mylar, ceramic, or other capacitor having low internal impedance at high frequencies should be chosen. The bypass capacitor should be mounted with shortest possible lead or track length directly across the regulator's input terminals. Figure 16 shows the ESR that allows the LDO to remain stable for various load currents.

Figure 16. ESR for Vout = 3.0V

## Applications should be tested over all operating conditions to insure stability.

#### THERMAL PROTECTION

Internal thermal limiting circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 150°C, the output is disabled. There is no hysteresis built into the thermal protection. As a result the output will appear to be oscillating during thermal limit. The output will turn off until the temperature drops below the 150°C then the output turns on again. The process will repeat if the junction increases above the threshold. This will continue until the existing conditions allow the junction to operate below the temperature threshold.

### Thermal limit is not a substitute for proper heatsinking.

The internal current limit will typically limit current to 450 mA. If during current limit the junction exceeds 150°C, the thermal protection will protect the device also. **Current limit is not a substitute for proper heatsinking.**

#### **OUTPUT NOISE**

In many applications it is desirable to reduce the noise present at the output. Reducing the regulator bandwidth by increasing the size of the output capacitor will reduce the noise.

#### **ORDERING INFORMATION**

| Device             | V <sub>O</sub> Typ (V)   | Operating Temperature<br>Range, Tolerance                                                          | Case  | Package              | Marking | Shipping <sup>†</sup> |

|--------------------|--------------------------|----------------------------------------------------------------------------------------------------|-------|----------------------|---------|-----------------------|

| MC33275DT-2.5RKG   | 2.5 V<br>(Fixed Voltage) | 1% Tolerance<br>at T <sub>A</sub> = 25°C                                                           | 369A  | DPAK<br>(Pb-Free)    | 27525G  | 2500/Tape & Reel      |

| MC33275D-3.0R2G    | 3.0 V<br>(Fixed Voltage) |                                                                                                    | 751   | SOIC-8<br>(Pb-Free)  | 27530   | 2500/Tape & Reel      |

| MC33275MN-3.0R2G   |                          | 2% Tolerance at<br>T <sub>J</sub> from -40°C to +125°C                                             | 488AF | DFN8<br>(Pb–Free)    | 27530   | 3000/Tape & Reel      |

| MC33275D-3.3R2G    | 3.3 V<br>(Fixed Voltage) | 1% Tolerance<br>at T <sub>A</sub> = 25°C                                                           | 751   | SOIC-8<br>(Pb-Free)  | 27533   | 2500/Tape & Reel      |

| MC33275DT-3.3RKG   |                          |                                                                                                    | 369A  | DPAK<br>(Pb-Free)    | 27533G  | 2500/Tape & Reel      |

| MC33275ST-3.3T3G   |                          | 2% Tolerance at                                                                                    | 318E  | SOT-223<br>(Pb-Free) | 27533   | 4000/Tape & Reel      |

| NCV33275ST3.3T3G*  |                          | $T_J$ from -40°C to +125°C<br>1% Tolerance<br>at $T_A = 25°C$                                      | 318E  | SOT-223<br>(Pb-Free) | 27533   | 4000/Tape & Reel      |

| MC33275D-5.0R2G    | 5.0 V<br>(Fixed Voltage) | 1% Tolerance<br>at T <sub>A</sub> = 25°C                                                           | 751   | SOIC-8<br>(Pb-Free)  | 27550   | 2500/Tape & Reel      |

| MC33275DT-5.0RKG   |                          |                                                                                                    | 369A  | DPAK<br>(Pb-Free)    | 27550G  | 2500/Tape & Reel      |

| MC33275ST-5.0T3G   |                          | 2% Tolerance at<br>T <sub>J</sub> from -40°C to +125°C<br>1% Tolerance<br>at T <sub>A</sub> = 25°C | 318E  | SOT-223<br>(Pb-Free) | 27550   | 4000/Tape & Reel      |

| NCV33275ST-5.0T3G* |                          |                                                                                                    | 318E  | SOT-223<br>(Pb-Free) | 27550   | 4000/Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable

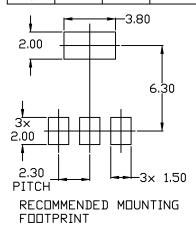

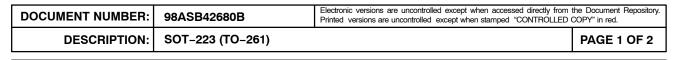

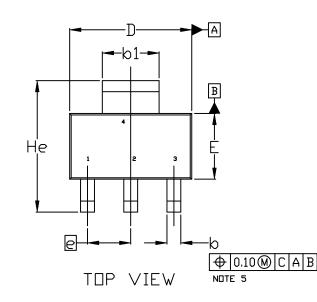

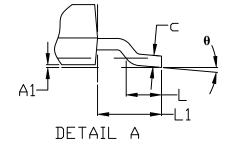

SOT-223 (TO-261) CASE 318E-04 ISSUE R

SEE DETAIL A

FRONT VIEW

DATE 02 OCT 2018

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS D & E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.200MM PER SIDE.

- 4. DATUMS A AND B ARE DETERMINED AT DATUM H.

- AI IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

- 6. POSITIONAL TOLERANCE APPLIES TO DIMENSIONS & AND &1.

|     | MILLIMETERS |          |             |  |  |

|-----|-------------|----------|-------------|--|--|

| DIM | MIN.        | NDM.     | MAX.        |  |  |

| A   | 1.50        | 1.63     | 1.75        |  |  |

| A1  | 0.02        | 0.06     | 0.10        |  |  |

| b   | 0.60        | 0.75     | 0.89        |  |  |

| b1  | 2.90        | 3.06     | 3.20        |  |  |

| с   | 0.24        | 0.29     | 0.35        |  |  |

| D   | 6.30        | 6.50     | 6.70        |  |  |

| E   | 3.30        | 3.50     | 3.70        |  |  |

| e   |             | 2.30 B2C | ;           |  |  |

| L   | 0.20        |          |             |  |  |

| L1  | 1.50        | 1.75     | 2.00        |  |  |

| He  | 6.70        | 7.00     | 7.30        |  |  |

| θ   | 0*          |          | 10 <b>°</b> |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

SCALE 1:1

#### SOT-223 (TO-261) CASE 318E-04 ISSUE R

#### DATE 02 OCT 2018

| STYLE 1:<br>PIN 1. BASE<br>2. COLLECTOR<br>3. EMITTER<br>4. COLLECTOR | STYLE 2:<br>PIN 1. ANODE<br>2. CATHODE<br>3. NC<br>4. CATHODE        | STYLE 3:<br>PIN 1. GATE<br>2. DRAIN<br>3. SOURCE<br>4. DRAIN           | Style 4:<br>Pin 1. Source<br>2. Drain<br>3. Gate<br>4. Drain   | STYLE 5:<br>PIN 1. DRAIN<br>2. GATE<br>3. SOURCE<br>4. GATE    |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| STYLE 6:<br>PIN 1. RETURN<br>2. INPUT<br>3. OUTPUT<br>4. INPUT        | STYLE 7:<br>PIN 1. ANODE 1<br>2. CATHODE<br>3. ANODE 2<br>4. CATHODE | STYLE 8:<br>CANCELLED                                                  | STYLE 9:<br>Pin 1. Input<br>2. Ground<br>3. Logic<br>4. Ground | STYLE 10:<br>PIN 1. CATHODE<br>2. ANODE<br>3. GATE<br>4. ANODE |

| STYLE 11:<br>PIN 1. MT 1<br>2. MT 2<br>3. GATE<br>4. MT 2             | Style 12:<br>Pin 1. Input<br>2. Output<br>3. NC<br>4. Output         | STYLE 13:<br>PIN 1. GATE<br>2. COLLECTOR<br>3. EMITTER<br>4. COLLECTOR |                                                                |                                                                |

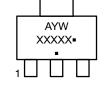

#### GENERIC MARKING DIAGRAM\*

- A = Assembly Location

- Y = Year

- W = Work Week

- XXXXX = Specific Device Code

- = Pb-Free Package

- (Note: Microdot may be in either location) \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42680B      | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOT-223 (TO-261) |                                                                                                                                                                                    | PAGE 2 OF 2 |  |  |  |

|                  |                  |                                                                                                                                                                                    |             |  |  |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi and ONSEMI: are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98AON15232D     | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DFN8, 4X4, 0.8P |                                                                                                                                                                                 | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor and 🔘 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the visibility of the advector and any and the other the size of the region of |                 |                                                                                                                                                                                 |             |  |  |  |

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repo<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SOIC-8 NB                                                                                                                                                                                |  | PAGE 1 OF 2 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                          |  |             |  |  |  |  |

| onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights or the rights of others. |                                                                                                                                                                                          |  |             |  |  |  |  |

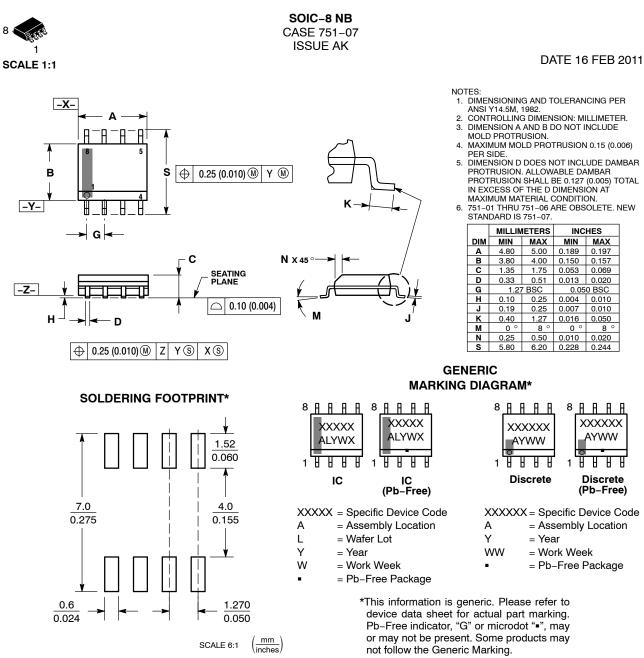

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE

6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK

7. VOULK 8. VIN

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                   | PAGE 2 OF 2 |  |  |  |

|                  |             |                                                                                                                                                                                   |             |  |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>